Power MOSFET

The power metal oxide semiconductor field-effect transistor (MOSFET) evolved from integrated circuit technology in the 1970s in response to the need to develop power transistors that can be controlled using much lower gate drive power levels compared to the existing power bipolar transistors. It offers performances unavailable from bipolar transistors and thyristors, thus promises to not only offer better replacements for present-day devices but also lead to new circuit and systems concepts and bring power electronics into new areas of applications. Typical uses include switching of linear power supplies, speed control of d.c. and a.c. motors, stepper motor controllers, relays, lighting controls, solenoid drivers, appliance controls, and induction-heating.

A power MOSFET is a voltage-controlled device and requires only a small input current. In this device, the control signal is applied to a metal gate electrode that is separated from the semiconductor surface by an intervening insulator, typically silicon dioxide. The control signal required is essentially a bias voltage with no significant steady-state gate current flow in either the on-state or the off-state. Even during the switching of the devices between these states, the gate current is small at typical operating frequencies because it only serves to charge and discharge the input gate capacitance, the high input impedance is a primary feature of the power MOSFET that greatly simplifies the gate drive circuitry and reduces the cost of the power-electronics.

The power MOSFET is a unipolar device. Current conduction occurs through transport of majority carriers in the drift region without the presence of minority carrier injection required for bipolar transistor operation. In this device, during turn-off, no delays are observed because of storage or recombination of minority carriers. Their inherent switching speed is orders of magnitude faster than that for bipolar transistors. This feature is particularly attractive in circuits operating at high frequencies where switching power losses are dominant. The power MOSFET having operating frequencies are well above 100 kHz. The power MOSFETs switching timing is in order of 50 – 100 nanoseconds and can generate many kilowatts of power at frequencies up to 500 kHz.

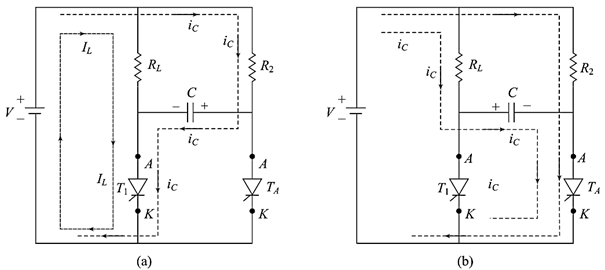

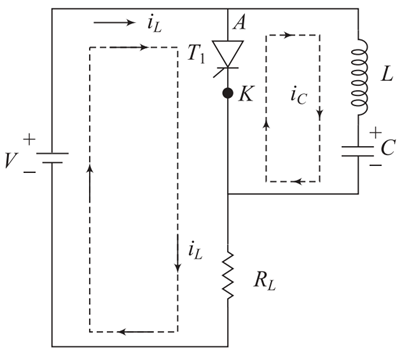

A power MOSFET is a four-layer semiconductor structure with alternate p-type and n-type doping. Figure 7 shows a vertically oriented enhancement mode n-channel power MOSFET which is a n+ p n– n+ structure. A power MOSFET consists of a parallel connection of many MOSFET cells in a single IC. The doping density in the two n+ end layers of a vertically oriented power MOSFET is the same, and its value is quite large, typically 1019 cm–3. One end is used as source and the other end (n+ substrate) is used as drain as depicted in Figure 7. The n– layer is epitaxially grown on the n+ substrate. Then p-type semiconductor is diffused in the epitaxially grown n– layer and the p region developed. After that n+ semiconductor is diffused in the p region and the n+ region is developed.

The n– layer is called the drain drift region and the doping density in the n– layer is low. The typical value of n– layer doping density is about 1014 cm–3 to 1015 cm–3. The thickness of n– drift region determines the breakdown voltage of the device. The p-type semiconductor layer is the region where the channel is established between source and drain. Therefore, p region is called the body of a transistor. The doping density of p region is about 1016 cm–3. This structure is known as vertical diffused MOSFET (VDMOS). A four-layer semiconductor structure with the opposite doping density of Figure 7 can also be manufactured and then the developed structure is called a p-channel MOSFET.

Figure 7

When the gate-to-source voltage is zero (VGS = 0), the current ID cannot flow from the drain to source terminals of MOSFET as any one of the pn junctions is reverse biased by the input voltage VDD. As the gate is isolated from the body (p region) by a layer of silicon dioxide (SiO2) which behaves as a very good insulator, the minority carriers cannot be injected into the p region through the gate terminal. When the gate to source voltage is greater than zero, the gate is positive with respect to the source, an electric field will be developed and an n channel is formed in the p region. Then the source is connected with drain through n channel and current ID flows from drain to source. If the gate-to-source voltage is increased, the drain current ID increases. The value of ID depends on the thickness of the silicon dioxide or gate oxide, the width of gate and the number of gate and source regions which are connected in parallel.

The circuit symbol of n channel power MOSFET and p-channel power MOSFET are depicted in Figure 8. The direction of the arrow represents the direction of current flow.

Figure 8

latest video

news via inbox

Nulla turp dis cursus. Integer liberos euismod pretium faucibua